# A 2.4 GHz Integrated CMOS Power Amplifier with Micromachined Inductors

Y. Emery Chen, Yong Kyu. Yoon, Joy Laskar, and Mark Allen

Microelectronics Research Center, and Yamacraw Design Center

School of Electrical and Computer Engineering

Georgia Institute of Technology

791 Atlantic Drive

Atlanta, Ga 30332, USA

**Abstract** — This paper reports the development of the first 2.4GHz monolithic-integrated CMOS power amplifier with micromachined inductors. The amplifier is implemented in a 0.24-mm CMOS technology. The high-*Q* (quality factor) micromachined solenoid inductors are fabricated on the surface of the CMOS chip. For 2.5-V operation, the amplifier delivers 20-dBm output power with 31% PAE (power added efficiency) to 50-W load.

## I. INTRODUCTION

The rapidly growing markets of wireless communication encourage the research and development of more cost-effective and compact transceivers. CMOS leverages digital VLSI technology and benefits from analog and RF IC designs. However, implementing high-*Q* inductors in standard CMOS technology is one of the technical bottlenecks for RF applications [1]. Recently, several CMOS RF amplifiers have been reported at 0.8 GHz and 1.9 GHz [2]-[5]. Most of these amplifiers are designed with off-chip components or LTCC (Low Temperature Co-fired Ceramics) passive components. Although the monolithic-integrated 1.9 GHz RF CMOS power amplifier is demonstrated with on-chip inductors and capacitors, the low-*Q* spiral inductors degrade the amplifier performance significantly [4].

The integration of Si active devices with advanced micromechanical (MEMS) devices and micromachined components on one wafer is considered the next step beyond the state-of-the-art in multi-chip module (MCM) for communication systems [6]-[7]. Many micromachined inductors have been reported to have much higher *Q* than the spiral inductors in CMOS technology [8]-[10]. To overcome the performance degradation due to lossy on-chip spiral inductors, the micromachined inductors can be post-processed and fabricated on the CMOS chips.

This paper reports the development of the 2.4 GHz monolithic-integrated CMOS power amplifier with micromachined solenoid inductors on the surface. The input and output are matched to 50  $\Omega$  on chip. The second harmonic tuning network is added at the output to improve the efficiency. For 2.5-V operation, the amplifier delivers 20-dBm output power with 31% PAE.

## II. MICROMACHINED SOLENOID INDUCTOR

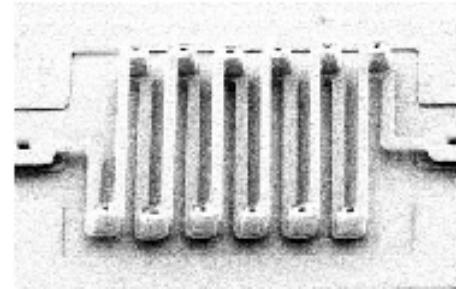

Fig. 1. Photograph of a micromachined 6-turn solenoid inductor.

The micromachined solenoid RF inductors are fabricated using thick photo resistive epoxy (SU-8) mold and Cu-electroplating technique on the Si substrate. The inductor coil is embedded in SU-8 mold. The embedding structure is mechanically robust and favorable for chip packaging. Since the inductance is characterized in the ambience of SU-8 mold, the inductor properties will remain the same after the packaging process. The solenoid coil is built on top of the 50- $\mu$ m thick SU-8 above the CMOS chip. The gap between the solenoid coil and the Si substrate helps to reduce the substrate energy loss at high frequency. The magnetic flux path of the coil is kept away from the Si substrate and the loss due to

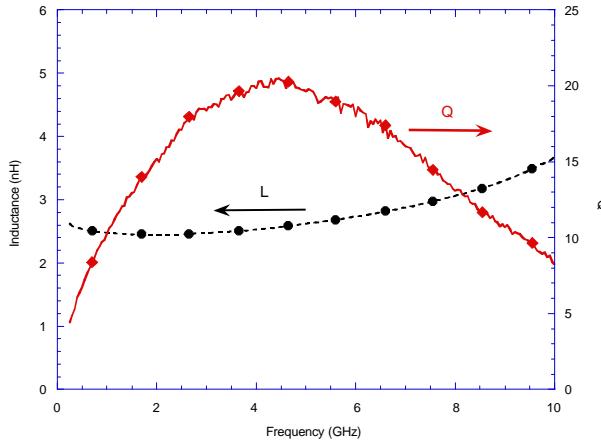

eddy current is also reduced. The cross-section area of the copper wire is  $20 \times 20 \mu\text{m}^2$  and the turn-to-turn pitch is  $80 \mu\text{m}$ . A micromachined 6-turn solenoid inductor is shown in Fig. 1. The measured quality factor and inductance of the inductor is shown in Fig. 2. The equivalent inductance,  $L$ , is about  $2.6 \text{ nH}$  and the peak  $Q$  is 21 at 4.5 GHz.

Fig. 2. Measured  $Q$  and  $L$  of the 6-turn micromachined solenoid inductor.

### III. POWER AMPLIFIER DESIGN

The power amplifier is implemented in a  $0.24\text{-}\mu\text{m}$  CMOS technology. There are five metal layers for flexible interconnection. This technology also provides the second poly layer to implement high- $Q$  poly-oxide-poly capacitors.

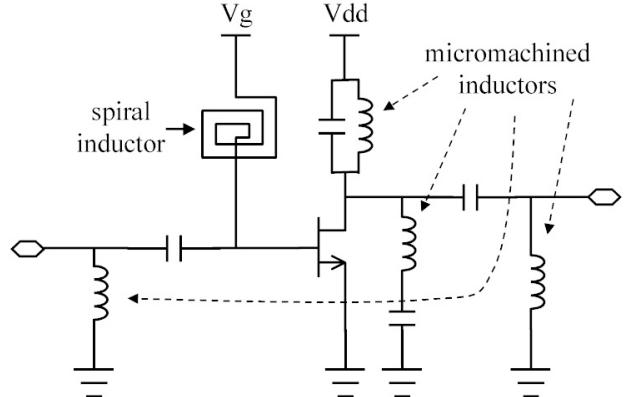

The schematic diagram of the amplifier is shown in Fig. 3. The topology of the power amplifier is single-stage common-source. The total gate width of the power transistor is  $2,400 \mu\text{m}$ . The transistor has 60 gate fingers and the gate width of the single gate finger is  $40 \mu\text{m}$ . The load impedance is determined by the load-pull measurement [11]. A modified BSIM3v3 model is developed for both large-signal and small-signal RF circuit simulation [12]. One spiral inductor is used at the gate of the transistor to provide the bias voltage. The spiral inductor is chosen instead of a micromachined inductor because the designed inductance is small and the spiral inductor does not degrade much the performance of power amplifier. In addition, the spiral inductor occupies less die area than the micromachined inductor and leads to more compact design. The other inductors on the chip are all micromachined inductors. They are used for matching and harmonic tuning. The  $Q$  of the inductors affect the power amplifier performance significantly, so

the high- $Q$  micromachined inductors are chosen. The second harmonic-tuning network is connected to the drain of the transistor to improve the efficiency of the power amplifier. The input and output matching networks match the amplifier to  $50 \Omega$  on chip and provide DC blocking at the same time. The capacitors used in matching and harmonic networks are poly-oxide-poly capacitors.

Fig. 3. Schematic diagram of the CMOS power amplifier.

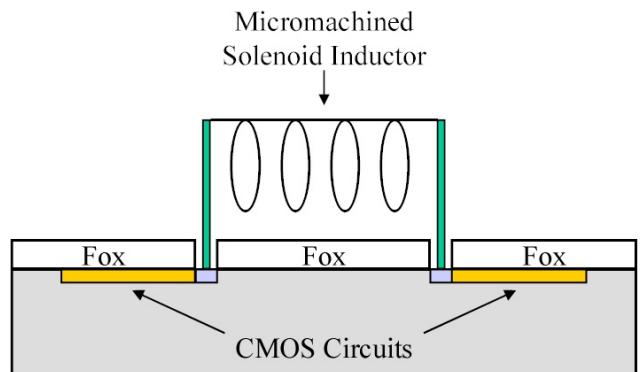

The CMOS circuitry is covered and protected by the passivation layer. There are passivation openings over the pads that are placed for the connection to the micromachined inductors. Fig. 4 shows the cross-section view of the CMOS power amplifier with the micromachined solenoid inductors on the surface.

Fig. 4. Cross-section view of the CMOS power amplifier with micromachined solenoid inductors on the surface.

### IV. RESULTS

The photograph of the CMOS power amplifier with micromachined solenoid inductors is shown in Fig. 5.

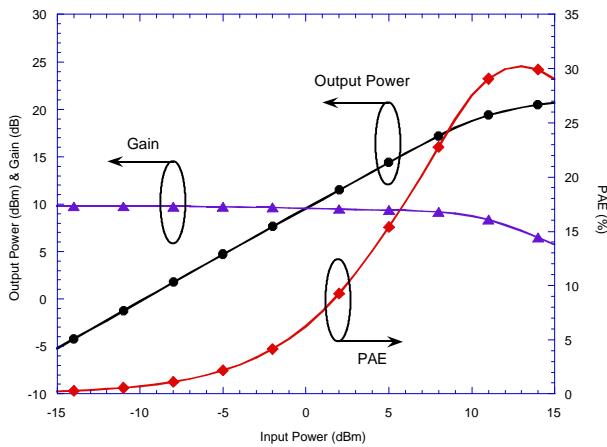

The total chip size is  $1,860 \times 1,180 \mu\text{m}^2$ . For  $V_{dd} = 2.5$  V, the power amplifier delivers 20-dBm output power with 31% PAE as biased at class AB. The output power, power gain, and PAE with respect to input power sweep are shown in Fig. 6. The input VSWR (Voltage Standing Wave Ratio) is 1.6 at 2.4 GHz. By incorporating the micromachined solenoid inductors on the CMOS RF circuits, the lossy on-chip spiral inductors can be avoided and the CMOS RFICs can also remain compact.

Fig. 5. Photograph of the CMOS power amplifier with micromachined solenoid inductors.

Fig. 6. Output power, power gain, and PAE of the CMOS power amplifier.

## V. CONCLUSION

The 2.4 GHz monolithic-integrated CMOS power amplifier is developed with the high- $Q$  micromachined solenoid inductors. The input and output of the amplifier are matched to  $50 \Omega$  on chip. For 2.5-V class AB operation, the amplifier delivers 20-dBm output power

with 31% PAE. The die size of the amplifier is  $1,860 \times 1,180 \mu\text{m}^2$ . The integration of CMOS RF circuits with micromachined components can be a potential solution for compact and high performance CMOS RFICs.

## ACKNOWLEDGEMENT

The authors would like to acknowledge National Semiconductor Corporation and Yamacraw Design Center for the foundry support and design assistance.

## REFERENCES

- [1] P. R. Gray, R. G. Meyer, "Future Directions in Silicon ICs for RF Personal Communications," *Proceedings, 1995 IEEE Custom Integrated Circuits Conference*, pp. 83-90, May 1995.

- [2] D. Su and W. McFarland, "A 2.5-V, 1-W Monolithic CMOS RF Power Amplifier," *Proceedings, 1997 IEEE Custom Integrated Circuits Conference*, pp. 189-192, 1997.

- [3] K. Tsai and P. Gray, "A 1.9GHz, 1-W CMOS Class-E Power Amplifier for Wireless Communications," *IEEE Journal of Solid-State Circuits*, vol. 34, no. 7, pp. 962-970, July 1999.

- [4] Y. J. E. Chen, M. Hamai, D. Heo, A. Sutono, S. Yoo, and J. Laskar, "RF Power Amplifier Integration in CMOS Technology," *2000 IEEE MTT-S Int. Microwave Symp. Dig.*, vol. 1, pp. 545-548, June 2000.

- [5] A. Giry, J-M. Fournier, and M. Pons, "A 1.9GHz Low Voltage CMOS Power Amplifier for Medium Power RF Applications," *2000 IEEE Radio Frequency Integrated Circuits Symposium, Digest*, pp. 121-124, June 2000.

- [6] L. Katehi, G. Rebeiz, and C. Nguyen, "MEMS and Si-Micromachined Components for Low-Power, High-Frequency Communications Systems," *1998 IEEE MTT-S Int. Microwave Symp. Dig.*, pp. 331-333, June 1998.

- [7] P. Asbeck, J. Mink, T. Itoh, G. Haddad, "Device and Circuit Approaches for Next-Generation Wireless Communications," *Microwave Journal*, Euro-Global Edition, vol. 42, no. 2, pp. 22-42, February 1999.

- [8] Y. Kim and M. Allen, "Surface Micromachined Solenoid Inductors for High Frequency Applications," *IEEE Trans. on Components, Packaging, and Manufacturing Technology – Part C*, vol. 21, no. 1, pp. 26-33, January 1998.

- [9] J-B Yoon, C-H Han, E. Yoon, and C-K Kim, "Monolithic High- $Q$  Overhang Inductors Fabricated on Silicon and Glass Substrates," *Technical Digest, IEDM*, pp. 753-756, December 1999.

- [10] P. Gammel, B. Barber, V. Lubecke, N. Belk, M. Frei, "Design, Test, and Simulation of Self-assembled Micromachined RF Inductors," *Proceedings of the SPIE – The International Society for Optical Engineering*, vol. 3680, pt. 1-2, pp. 582-591, 1999.

- [11] E. Chen, D. Heo, M. Hamai, J. Laskar, and D. Bien, "0.24- $\mu\text{m}$  CMOS Technology for Bluetooth Power Applications," *Proceedings, 2000 IEEE Radio and Wireless Conference*, pp. 163-166, September 2000.

[12] E. Chen, D. Heo, J. Laskar, and D. Bien, "0.24- $\mu$ m CMOS Technology and BSIM RF Modeling for Bluetooth Power Applications," *Microwave Journal*, vol. 44, no. 2, pp. 142-152, February 2001.